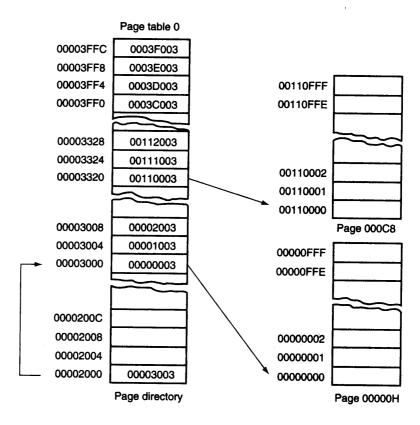

FIGURE 2–14 The page directory, page table 0, and two memory pages. Note how the address of page 000C8000–000C9000 has been moved to 00110000–00110FFF.

the Pentium and Pentium Pro microprocessors, pages can be either 4K bytes in length or 4M bytes in length. Although no software currently supports the 4M-byte pages, as the Pentium 4 and more advanced versions pervade the personal computer, operating systems of the future will undoubtedly begin to support 4M-byte memory pages.

## 2-5 SUMMARY

- 1. The programming model of the 8086 through 80286 contains 8- and 16-bit registers. The programming model of the 80386 and above contains 8-, 16-, and 32-bit extended registers as well as two additional 16-bit segment registers: FS and GS.

- 2. The 8-bit registers are AH, AL, BH, BL, CH, CL, DH, and DL. The 16-bit registers are AX, BX, CX, DX, SP, BP, DI, and SI. The segment registers are CS, DS, ES, SS, FS, and GS. The 32-bit extended registers are EAX, EBX, ECX, EDX, ESP, EBP, EDI, and ESI. In addition, the microprocessor contains an instruction pointer (IP/EIP) and flag register (FLAGS or EFLAGS).

- 3. All real mode memory addresses are a combination of a segment address plus an offset address. The starting location of a segment is defined by the 16-bit number in the segment register that is appended with a hexadecimal zero at its rightmost end. The offset address is a 16-bit number added to the 20-bit segment address to form the real mode memory address.

- 4. All instructions (code) are accessed by the combination of CS (segment address) plus IP or EIP (offset address).

- 5. Data are normally referenced through a combination of the DS (data segment), and either an offset address or the contents of a register that contains the offset address. The 8086 through the Pentium 4 use BX, DI, and SI as default offset registers for data if 16-bit registers are selected. The 80386 and above can use the 32-bit registers EAX, EBX, ECX, EDX, EDI, and ESI as default offset registers for data.

- 6. Protected mode operation allows memory above the first 1M byte to be accessed by the 80286 through the Pentium 4 microprocessors. This extended memory system (XMS) is accessed via a segment address plus an offset address, just as in the real mode. The difference is that the segment address is not held in the segment register. In the protected mode, the segment starting address is stored in a descriptor that is selected by the segment register.

- 7. A protected mode descriptor contains a base address, limit, and access rights byte. The base address locates the starting address of the memory segment; the limit defines the last location of the segment. The access rights byte defines how the memory segment is accessed via a program. The 80286 microprocessor allows a memory segment to start at any of its 16M bytes of memory using a 24-bit base address. The 80386 and above allow a memory segment to begin at any of its 4G bytes of memory using a 32-bit base address. The limit is a 16-bit number in the 80286 and a 20-bit number in the 80386 and above. This allows an 80286 memory segment limit of 64K bytes, and an 80386 and above memory segment limit of either 1M bytes (G = 0) or 4G bytes (G = 1).

- 8. The segment register contains three fields of information in the protected mode. The leftmost 13 bits of the segment register address one of 8192 descriptors from a descriptor table. The TI bit accesses either the global descriptor table (TI = 0) or the local descriptor table (TI = 1). The rightmost 2 bits of the segment register select the requested priority level for the memory segment access.

- 9. The program-invisible registers are used by the 80286 and above to access the descriptor tables. Each segment register contains a cache portion that is used in protected mode to hold the base address, limit, and access rights acquired from a descriptor. The cache allows the microprocessor to access the memory segment without again referring to the descriptor table until the segment register's contents are changed.

- 10. A memory page is 4K bytes in length. The linear address, as generated by a program, can be mapped to any physical address through the paging mechanism found within the 80386 through the Pentium 4 microprocessor.

- 11. Memory paging is accomplished through control registers CR0 and CR3. The PG bit of CR0 enables paging and the contents of CR3 addresses the page directory. The page directory contains up to 1024 page table addresses that are used to access paging tables. The page table contains 1024 entries that locate the physical address of a 4K-byte memory page.

- 12. The TLB (translation look-aside buffer) caches the 32 most recent page table translations. This precludes page table translation if the translation resides in the TLB, speeding the execution of software.

# 2-6 QUESTIONS AND PROBLEMS

- 1. What are program-visible registers?

- 2. The 80286 addresses registers that are 8- and \_\_\_\_\_ bits wide.

- 3. The extended registers are addressable by which microprocessors?

- 4. The extended BX register is addressed as \_\_\_\_\_

- 5. Which register holds a count for some instructions?

- 6. What is the purpose of the IP/EIP register?

- 7. The carry flag bit is set by which arithmetic operations?

- 8. Will an overflow occur if a signed FFH is added to a signed 01H?

- 9. A number that contains 3 one bits is said to have \_\_\_\_\_ parity.

- 10. Which flag bit controls the INTR pin on the microprocessor?

2–6 QUESTIONS AND PROBLEMS 53

- 11. Which microprocessors contain an FS segment register?

- 12. What is the purpose of a segment register in the real mode operation of the microprocessor?

- 13. In the real mode, show the starting and ending addresses of each segment located by the following segment register values:

- (a) 1000H

- (b) 1234H

- (c) 2300H

- (d) E000H

- (e) AB00H

- 14. Find the memory address of the next instruction executed by the microprocessor, when operated in the real mode, for the following CS:IP combinations:

- (a) CS = 1000H and IP = 2000H

- (b) CS = 2000H and IP = 1000H

- (c) CS = 2300H and IP = 1A00H

- (d) CS = 1A00H and IP = B000H

- (e) CS = 3456H and IP = ABCDH

- 15. Real mode memory addresses allow access to memory below which memory address?

- 16. Which register or registers are used as an offset address for string instruction destinations in the micro-processor?

- 17. Which 32-bit register or registers are used as an offset address for data segment data in the Pentium 4 microprocessor?

- 18. The stack memory is addressed by a combination of the \_\_\_\_\_ segment plus \_\_\_\_\_ offset

- 19. If the base pointer (BP) addresses memory, the \_\_\_\_\_ segment contains the data.

- 20. Determine the memory location addressed by the following real mode 80286 register combinations:

- (a) DS = 1000H and DI = 2000H

- (b) DS = 2000H and SI = 1002H

- (c) SS = 2300H and BP = 3200H

- (d) DS = A000H and BX = 1000H

- (e) SS = 2900H and SP = 3A00H

- 21. Determine the memory location addressed by the following real mode Pentium 4 register combinations:

- (a) DS = 2000H and EAX = 00003000H

- (b) DS = 1A00H and ECX = 00002000H

- (c) DS = C000H and ESI = 0000A000H

- (d) SS = 8000H and ESP = 00009000H

- (e) DS = 1239H and EDX = 0000A900H

- 22. Protected mode memory addressing allows access to which area of the memory in the 80286 microprocessor?

- 23. Protected mode memory addressing allows access to which area of the memory in the Pentium 4 microprocessor?

- 24. What is the purpose of the segment register in protected mode memory addressing?

- 25. How many descriptors are accessible in the global descriptor table in the protected mode?

- 26. For an 80286 descriptor that contains a base address of A00000H and a limit of 1000H, what starting and ending locations are addressed by this descriptor?

- 27. For an 80486 descriptor that contains a base address of 01000000H, a limit of 0FFFFH, and G = 0, what starting and ending locations are addressed by this descriptor?

- 28. For a Pentium 4 descriptor that contains a base address of 00280000H, a limit of 00010H, and G = 1, what starting and ending locations are addressed by this descriptor?

- 29. If the DS register contains 0020H in a protected mode system, which global descriptor table entry is accessed?

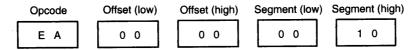

- 30. If DS = 0103H in a protected mode system, the requested privilege level is \_\_\_\_\_

- 31. If DS = 0105H in a protected mode system, which entry, table, and requested privilege level are selected?

- 32. What is the maximum length of the global descriptor table in the Pentium 4 microprocessor?

#### CHAPTER 2 THE MICROPROCESSOR AND ITS ARCHITECTURE 54

- 33. Code a descriptor that describes a memory segment that begins at location 210000H and ends at location 21001FH. This memory segment is a code segment that can be read. The descriptor is for an 80286 microprocessor.

- 34. Code a descriptor that describes a memory segment that begins at location 03000000H and ends at location 05FFFFFFH. This memory segment is a data segment that grows upward in the memory system and can be written. The descriptor is for an 80386 microprocessor.

- 35. Which register locates the global descriptor table?

- 36. How is the local descriptor table addressed in the memory system?

- 37. Describe what happens when a new number is loaded into a segment register when the microprocessor is operated in the protected mode.

- 38. What are the program-invisible registers?

- 39. What is the purpose of the GDTR?

- 40. How many bytes are found in a memory page?

- 41. What register is used to enable the paging mechanism in the 80386, 80486, Pentium, Pentium Pro, and Pentium 4 microprocessors?

- 42. How many 32-bit addresses are stored in the page directory?

- 43. Each entry in the page directory translates how much linear memory into physical memory?

- 44. If the microprocessor sends linear address 00200000H to the paging mechanism, which paging directory entry is accessed, and which page table entry is accessed?

- 45. What value is placed in the page table to redirect linear address 20000000H-30000000H?

- 46. What is the purpose of the TLB located within the 80486 microprocessor?

- 47. Using the Internet, write a short report that details the TLB. Hint: You might want to go to the Intel Web site and search for information.

# **CHAPTER 3**

# **Addressing Modes**

| SRINIVAS<br>PG MANAGE<br>ACC No.: | MENT | STUBIES |

|-----------------------------------|------|---------|

| CALL No.:                         |      |         |

#### INTRODUCTION

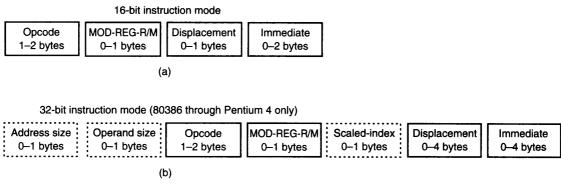

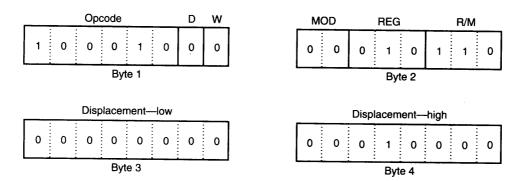

Efficient software development for the microprocessor requires a complete familiarity with the addressing modes employed by each instruction. In this chapter, the MOV (move data) instruction is used to describe the data-addressing modes. The MOV instruction transfers bytes or words of data between registers, or between registers and memory in the 8086 through the 80286 and bytes, words, or doublewords in the 80386 and above. In describing the program memory-addressing modes, the CALL and JUMP instructions show how to modify the flow of the program.

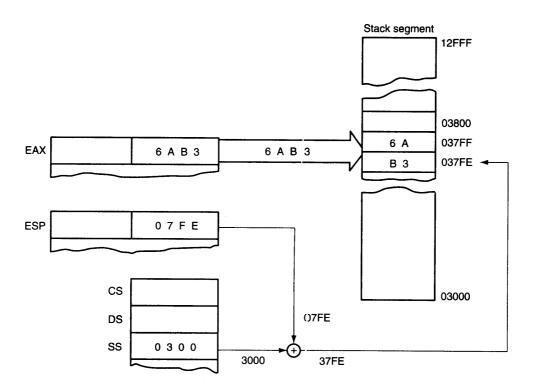

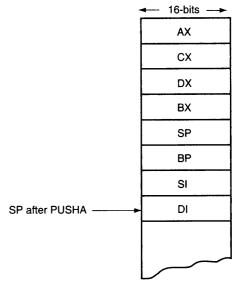

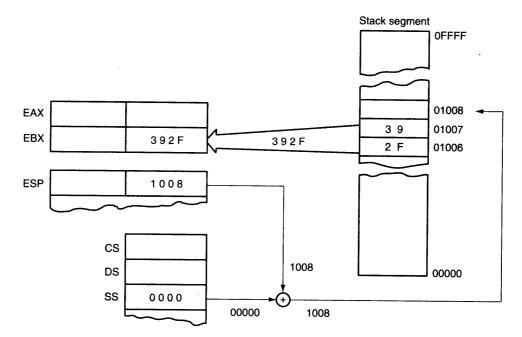

The data-addressing modes include register, immediate, direct, register indirect, base-plus-index, register relative, and base relative-plus-index in the 8086 through the 80286 microprocessor. The 80386 and above also include a scaled-index mode of addressing memory data. The program memory-addressing modes include program relative, direct, and indirect. The operation of the stack memory is explained so that the PUSH and POP instructions are understood.

#### **CHAPTER OBJECTIVES**

Upon completion of this chapter, you will be able to:

- 1. Explain the operation of each data-addressing mode.

- 2. Use the data-addressing modes to form assembly language statements.

- 3. Explain the operation of each program memory-addressing mode.

- 4. Use the program memory-addressing modes to form assembly and machine language statements.

- 5. Select the appropriate addressing mode to accomplish a given task.

- 6. Detail the difference between addressing memory data using real mode and protected mode operation.

- 7. Describe the sequence of events that place data onto the stack or remove data from the stack.

- 8. Explain how a data structure is placed in memory and used with software.

# 3-1 DATA-ADDRESSING MODES

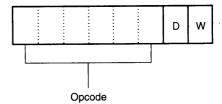

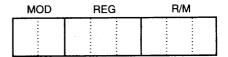

Because the MOV instruction is a common and flexible instruction, it provides a basis for the explanation of the data-addressing modes. Figure 3–1 illustrates the MOV instruction and defines the direction of data flow. The source is to the right and the destination is to the left, next to the opcode MOV. (An opcode, or operation code, tells the microprocessor which operation to perform.) This direction of flow, which is applied to all instructions, is awkward at first. We naturally assume that things move from left to right, whereas here they move from right to left. Notice that a comma always separates the destination from the source in an instruction. Also, note that memory-to-memory transfers are not allowed by any instruction except for the MOVS instruction.

In Figure 3–1, the MOV AX,BX instruction transfers the word contents of the source register (BX) into the destination register (AX). The source never changes, but the destination usually changes.<sup>1</sup> It is essential to remember that a MOV instruction always *copies* the source data and into the destination. The MOV never actually picks up the data and moves it. Also, note that the flag register remains unaffected by most data transfer instructions. The source and destination are often called **operands**.

FIGURE 3–1 The MOV instruction showing the source, destination, and direction of data flow.

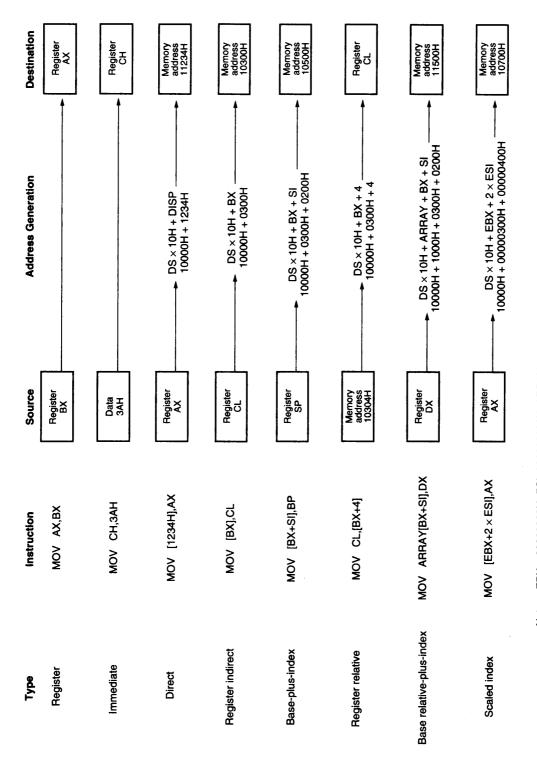

Figure 3–2 shows all possible variations of the data-addressing modes using the MOV instruction. This illustration helps to show how each data-addressing mode is formulated with the MOV instruction and also serves as a reference. Note that these are the same data-addressing modes found with all versions of the Intel microprocessor, except for the scaled-index-addressing mode, which is found only in the 80386 through the Pentium 4. The data-addressing modes are as follows:

| Regi | ister   |

|------|---------|

| addı | ressing |

Transfers a copy of a byte or word from the source register or memory location to the destination register or memory location. (Example: the MOV CX,DX instruction copies the word-sized contents of register DX into register CX.) In the 80386 and above, a doubleword can be transferred from the source register or memory location to the destination register or memory location. (Example: the MOV ECX,EDX instruction copies the doubleword-sized contents of register EDX into register ECX.)

# Immediate addressing

Transfers the source-immediate byte or word of data into the destination register or memory location. (Example: the MOV AL,22H instruction copies a byte-sized 22H into register AL.) In the 80386 and above, a doubleword of immediate data can be transferred into a register or memory location. (Example: the MOV EBX,12345678H instruction opies a doubleword-sized 12345678H into the 32-bit wide EBX register.)

# Direct addressing

Moves a byte or word between a memory location and a register. The instruction set does not support a memory-to-memory transfer, except for the MOVS instruction. (Example: the MOV CX,LIST instruction copies the word-sized contents of memory location LIST into register CX.) In the 80386 and above, a doubleword-sized memory location can also be addressed. (Example: the MOV ESI,LIST instruction copies a 32-bit number, stored in four consecutive bytes of memory, from location LIST into register ESI.)

# Register indirect addressing

Transfers a byte or word between a register and a memory location addressed by an index or base register. The index and base registers are BP, BX, DI, and SI. (Example: the MOV AX,[BX] instruction copies the word-sized data from the data segment offset address indexed by BX into register AX.) In the 80386 and above, a

<sup>&</sup>lt;sup>1</sup>The exceptions are the CMP and TEST instructions, which never change the destination. These instructions are described in later chapters.

Notes: EBX = 00000300H, ESI = 00000200H, ARRAY = 1000H, and DS = 1000H

FIGURE 3-2 8086-Pentium 4 data-addressing modes.

byte, word, or double-word is transferred between a register and a memory location addressed by any register: EAX, EBX, ECX, EDX, EBP, EDI, or ESI. (Example: the MOV AL,[ECX] instruction loads AL from the data segment offset address selected by the contents of ECX.)

# Base-plus-index addressing

Transfers a byte or word between a register and the memory location addressed by a base register (BP or BX) plus an index register (DI or SI). (Example: the MOV [BX+DI],CL instruction copies the byte-sized contents of register CL into the data segment memory location addressed by BX plus DI.) In the 80386 and above, any register EAX, EBX, ECX, EDX, EBP, EDI, or ESI may be combined to generate the memory address. (Example: the MOV [EAX+EBX],CL instruction copies the byte-sized contents of register CL into the data segment memory location addressed by EAX plus EBX.)

# Register relative addressing

Moves a byte or word between a register and the memory location addressed by an index or base register plus a displacement. (Example: MOV AX,[BX+4] or MOV AX,ARRAY[BX]. The first instruction loads AX from the data segment address formed by BX plus 4. The second instruction loads AX from the data segment memory location in ARRAY plus the contents of BX.) The 80386 and above use any register to address memory. (Example: MOV AX,[ECX+4] or MOV AX,ARRAY[EBX]. The first instruction loads AX from the data segment address formed by ECX plus 4. The second instruction loads AX from the data segment memory location ARRAY plus the contents of EBX.)

#### Base relative-plusindex addressing

Transfers a byte or word between a register and the memory location addressed by a base and an index register plus a displacement. (Example: MOV AX,ARRAY[BX+DI] or MOV AX,[BX+DI+4]. These instructions load AX from a data segment memory location. The first instruction uses an address formed by adding ARRAY, BX, and DI and the second by adding BX, DI, and 4.) In the 80386 and above, MOV EAX,ARRAY[EBX+ECX] loads EAX from the data segment memory location accessed by the sum of ARRAY, EBX, and ECX.

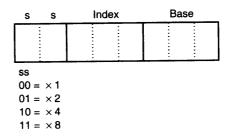

# Scaled-index addressing

Is available only in the 80386 through the Pentium 4 microprocessor. The second register of a pair of registers is modified by the scale factor of 2X, 4X, or 8X to generate the operand memory address. (Example: a MOV EDX,[EAX+4\*EBX] instruction loads EDX from the data segment memory location addressed by EAX plus 4 times EBX.) Scaling allows access to word (2X), doubleword (4X), or quadword (8X) memory array data. Note that a scaling factor of 1X also exists, but it is normally implied and does not appear in the instruction. The MOV AL,[EBX+ECX] is an example in which the scaling factor is a one. Alternately, the instruction can be rewritten as MOV AL,[EBX+1\*ECX]. Another example is a MOV AL,[2\*EBX] instruction, which uses only one scaled register to address memory.

# **Register Addressing**

Register addressing is the most common form of data addressing and, once the register names are learned, is the easiest to apply. The microprocessor contains the following 8-bit registers used with register addressing: AH, AL, BH, BL, CH, CL, DH, and DL. Also present are the following 16-bit registers: AX, BX, CX, DX, SP, BP, SI, and DI. In the 80386 and above, the extended 32-bit registers are EAX, EBX, ECX, EDX, ESP, EBP, EDI, and ESI. With register addressing, some MOV instructions, and the PUSH and POP instructions, also use the 16-bit segment registers (CS, ES, DS, SS, FS, and GS). It is important for instructions to use registers that are the same size. *Never* mix an 8-bit register with a 16-bit register, an 8-bit register with a 32-bit register, or a 16-bit register with 32-bit register because this is not allowed by the microprocessor and results in an error when assembled. This is

| Assembly Language | Size    | Operation                                                                   |

|-------------------|---------|-----------------------------------------------------------------------------|

| MOV AL,BL         | 8-bits  | Copies BL into AL                                                           |

| MOV CH,CL         | 8-bits  | Copies CL into CH                                                           |

| MOV AX,CX         | 16-bits | Copies CX into AX                                                           |

| MOV SP,BP         | 16-bits | Copies BP into SP                                                           |

| MOV DS,AX         | 16-bits | Copies AX into DS                                                           |

| MOV SI,DI         | 16-bits | Copies DI into SI                                                           |

| MOV BX,ES         | 16-bits | Copies ES into BX                                                           |

| MOV ECX,EBX       | 32-bits | Copies EBX into ECX                                                         |

| MOV ESP,EDX       | 32-bits | Copies EDX into ESP                                                         |

| MOV ES,DS         |         | Not allowed (segment-to-segment)                                            |

| MOV BL,DX         |         | Not allowed (mixed sizes)                                                   |

| MOV CS,AX         | _       | Not allowed (the code segment register may not be the destination register) |

**TABLE 3–1** Examples of the register-addressed instructions.

even true when a MOV AX,AL or a MOV EAX,AL instruction may seem to make sense. Of course, the MOV AX,AL or MOV EAX,AL instruction is *not* allowed because these registers are of different sizes. Note that a few instructions, such as SHL DX,CL, are exceptions to this rule, as indicated in later chapters. It is also important to note that *none* of the MOV instructions affect the flag bits.

Table 3–1 shows many variations of register move instructions. It is impossible to show all combinations because there are too many. For example, just the 8-bit subset of the MOV instruction has 64 different variations. A segment-to-segment register MOV instruction is about the only type of register MOV instruction *not* allowed. Note that the code segment register is not normally changed by a MOV instruction because the address of the next instruction is found in both IP/EIP and CS. If only CS were changed, the address of the next instruction would be unpredictable. Therefore, changing the CS register with a MOV instruction is not allowed.

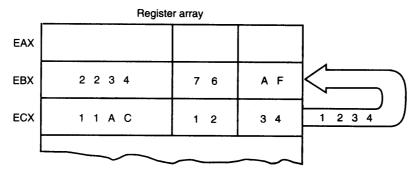

Figure 3-3 shows the operation of the MOV BX,CX instruction. Note that the source register's contents do not change, but the destination register's contents do change. The instruction moves (copies) a 1234H from register CX into register BX. This erases the old contents (76AFH) of register BX, but the contents of CX remain unchanged. The contents of the destination register or destination memory location change for all instructions

**FIGURE 3–3** The effect of executing the MOV BX, CX instruction at the point just before the BX register changes. Note that only the rightmost 16 bits of register EBX change.

except the CMP and TEST instructions. Note that the MOV BX,CX instruction does not affect the leftmost 16 bits of register EBX.

Example 3–1 shows a sequence of assembled instructions that copy various data between 8-, 16-, and 32-bit registers. As mentioned, the act of moving data from one register to another only changes the destination register, never the source. The last instruction in this example (MOV CS,AX) assembles without error, but causes problems if executed. If only the contents of CS change without changing IP, the next step in the program is unknown and therefore causes the program to go awry.

#### **EXAMPLE 3-1**

| 0000 8B C3<br>0002 8A CE<br>0004 8A CD<br>0006 66 8B C3<br>0009 66 8B D8<br>000C 66 8B C8 | MOV AX,BX MOV CL,DH MOV CL,CH MOV EAX,EBX MOV EBX,EAX MOV ECX,EAX | copy contents of BX into AX; copy the contents of DH into CL; copy the contents of CH into CL; copy the contents of EBX into EAX; copy EAX into EBX, ECX, and EDX |

|-------------------------------------------------------------------------------------------|-------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 000F 66 8B D0                                                                             | MOV EDX, EAX                                                      | an laba pa                                                                                                                                                        |

| 0012 8C C8<br>0014 8E D8                                                                  | MOV AX,CS<br>MOV DS,AX                                            | ;copy CS into DS                                                                                                                                                  |

| 0014 8E D8                                                                                | MOV CS, AX                                                        | ;assembles, but will cause problems                                                                                                                               |

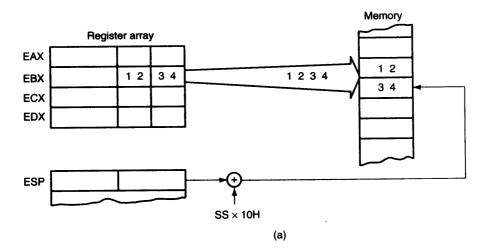

### **Immediate Addressing**

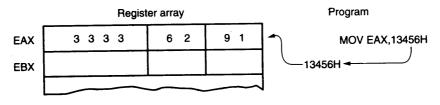

Another data-addressing mode is immediate addressing. The term *immediate* implies that the data immediately follow the hexadecimal opcode in the memory. Also note that immediate data are **constant data**, while the data transferred from a register are **variable data**. Immediate addressing operates upon a byte or word of data. In the 80386 through the Pentium 4 microprocessors, immediate addressing also operates on doubleword data. The MOV immediate instruction transfers a copy of the immediate data into a register or a memory location. Figure 3–4 shows the operation of a MOV EAX,13456H instruction. This instruction copies the 13456H from the instruction, located in the memory immediately following the hexadecimal opcode, into register EAX. As with the MOV instruction illustrated in Figure 3–3, the source data overwrites the destination data.

In symbolic assembly language, the symbol # precedes immediate data in some assemblers.<sup>2</sup> The MOV AX,#3456H instruction is an example. Most assemblers do not use the # symbol, but represent immediate data as in the MOV AX,3456H instruction. In this text, the # symbol is not used for immediate data. The most common assemblers—Intel ASM, Microsoft MASM,<sup>3</sup> and Borland TASM<sup>4</sup>—do not use the # symbol for immediate data, but an older assembler used with some Hewlett-Packard logic development systems do, as may others.

The symbolic assembler portrays immediate data in many ways. The letter H appends hexadecimal data. If hexadecimal data begin with a letter, the assembler requires that the data start with a 0. For example, to represent

**FIGURE 3–4** The operation of the MOV EAX,3456H instruction. This instruction copies the immediate data (13456H) into EAX.

<sup>&</sup>lt;sup>2</sup>This is true for the assembler provided by Hewlett-Packard in some development systems.

<sup>&</sup>lt;sup>3</sup>MASM (MACRO assembler) is a trademark of Microsoft Corporation.

<sup>&</sup>lt;sup>4</sup>TASM (Turbo assembler) is a trademark of Borland Corporation.

**TABLE 3–2** Examples of immediate addressing using the MOV instruction.

| Assembly Language                                                                                                                     | Size                                                                | Operation                                                                                                                                                                                                                             |

|---------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MOV BL,44<br>MOV AX,44H<br>MOV SI,0<br>MOV CH,100<br>MOV AL,'A'<br>MOV AX,'AB'<br>MOV CL,11001110B<br>MOV EBX,12340000H<br>MOV ESI,12 | 8-bits 16-bits 16-bits 8-bits 8-bits 16-bits 8-bits 32-bits 32-bits | Copies a 44 decimal (2CH) into BL Copies a 0044H into AX Copies a 0000H into SI Copies a 100 decimal (64H) into CH Copies an ASCII A into AL Copies an ASCII BA* into AX Copies a 11001110 binary into CL Copies a 12340000H into EBX |

| MOV EAX,100Y                                                                                                                          | 32-bits                                                             | Copies a 12 decimal into ESI Copies a 100 binary into EAX                                                                                                                                                                             |

<sup>\*</sup>Note: This is not an error. The ASCII characters are stored as a BA, so care should be exercised when using a word-sized pair of ASCII characters.

a hexadecimal F2, a 0F2H is used in assembly language. In some assemblers (though not in MASM, TASM, or this text), hexadecimal data are represented with an 'h, as in MOV AX,#'h1234. Decimal data are represented as is and require no special codes or adjustments. (An example is the 100 decimal in the MOV AL,100 instruction.) An ASCII-coded character or characters may be depicted in the immediate form if the ASCII data are enclosed in apostrophes. (An example is the MOV BH,'A' instruction, which moves an ASCII-coded A (41H) into register BH.) Be careful to use the apostrophe (') for ASCII data and not the single quotation mark ('). Binary data are represented if the binary number is followed by the letter B, or, in some assemblers, the letter Y. Table 3–2 shows many different variations of MOV instructions that apply immediate data.

Example 3–2 shows various immediate instructions in a short program that places a 0000H into the 16-bit registers AX, BX, and CX. This is followed by instructions that use register addressing to copy the contents of AX into registers SI, DI, and BP. This is a complete program that uses programming models for assembly and execution. The .MODEL .TINY statement directs the assembler to assemble the program into a single code segment. The .CODE statement or directive indicates the start of the code segment; the .STARTUP statement indicates the starting instruction in the program; and the .EXIT statement causes the program to exit to DOS. The END statement indicates the end of the program file. This program is assembled with MASM and executed with CodeView<sup>5</sup> (CV) to view its execution. Note that the most recent version of TASM will also accept MASM code. To store the program into the system use either the DOS EDIT program or Programmer's WorkBench<sup>6</sup> (PWB). Note that a TINY program always assembles as a command (.COM) program.

#### **EXAMPLE 3-2**

| 0000                                         | .MODEL TINY<br>.CODE                 | choose single segment model; indicate start of code segment    |

|----------------------------------------------|--------------------------------------|----------------------------------------------------------------|

|                                              | .STARTUP                             | ;indicate start of program                                     |

| 0100 B8 0000<br>0103 BB 0000<br>0106 B9 0000 | MOV AX,0<br>MOV BX,0000H<br>MOV CX,0 | ;place 0000H into AX ;place 0000H into BX ;place 0000H into CX |

<sup>&</sup>lt;sup>5</sup>CodeView is a registered trademark of Microsoft Corporation.

<sup>&</sup>lt;sup>6</sup>Programmer's WorkBench is a registered trademark of Microsoft Corporation.

#### 62 CHAPTER 3 ADDRESSING MODES

```

; copy AX into SI

MOV

SI.AX

0109 8B F0

;copy AX into DI

010B

8B F8

MOV

DI,AX

010D 8B E8

MOV

BP,AX

;copy AX into BP

;exit to DOS

.EXIT

;end of file

END

```

Each statement in a program consists of four parts or fields, as illustrated in Example 3–3. The leftmost field is called the *label* and it is used to store a symbolic name for the memory location that it represents. All labels must begin with a letter or one of the following special characters: @, \$, \_, or ?. A label may be of any length from 1 to 35 characters. The label appears in a program to identify the name of a memory location for storing data and for other purposes that are explained as they appear. The next field is called the *opcode field*; it is designed to hold the instruction, or opcode. The MOV part of the move data instruction is an example of an opcode. To the right of the opcode field is the *operand field*, which contains information used by the opcode. For example, the MOV AL,BL instruction has the opcode MOV and operands AL and BL. Note that some instructions contain between zero and three operands. The final field, the *comment field*, contains a comment about an instruction or a group of instructions. A comment always begins with a semicolon (;).

#### **EXAMPLE 3-3**

| LABEL          | OPCODE            | OPERAND                     | COMMENT                                                         |

|----------------|-------------------|-----------------------------|-----------------------------------------------------------------|

| DATA1<br>DATA2 | DB<br>DW          | 23H<br>1000H                | ;define DATA1 as a byte of 23H ;define DATA2 as a word of 1000H |

| START:         | MOV<br>MOV<br>MOV | AL, BL<br>BH, AL<br>CX, 200 | copy BL into AL; copy AL into BH; copy 200 decimal into CX      |

When the program is assembled and the **list** (.LST) file is viewed, it appears as the program listed in Example 3–2. The hexadecimal number at the far left is the offset address of the instruction or data. This number is generated by the assembler. The number or numbers to the right of the offset address are the machine-coded instructions or data that are also generated by the assembler. For example, if the instruction MOV AX,0 appears in a file and it is assembled, it appears in offset memory location 0100 in Example 3–2. Its hexadecimal machine language form is B8 0000. The B8 is the opcode in machine language and the 0000 is the 16-bit wide data with a value of zero. When the program was written, only the MOV AX,0 was typed into the editor; the assembler generated the machine code and addresses, and stored the program in a file ending with the extension .LST. Note that all programs shown in this text are in the form generated by the assembler.

# **Direct Data Addressing**

Most instructions can use the direct data-addressing mode. In fact, direct data addressing is applied to many instructions in a typical program. There are two basic forms of direct data addressing: (1) **direct addressing**, which applies to a MOV between a memory location and AL, AX, or EAX, and (2) **displacement addressing**, which applies to almost any instruction in the instruction set. In either case, the address is formed by adding the displacement to the default data segment address or an alternate segment address.

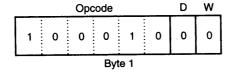

**Direct Addressing.** Direct addressing with a MOV instruction transfers data between a memory location, located within the data segment, and the AL (8-bit), AX (16-bit), or EAX (32-bit) register. A MOV instruction using this type of addressing is usually a 3-byte long instruction. (In the 80386 and above, a register size prefix may appear before the instruction, causing it to exceed three bytes in length.)

The MOV AL, DATA instruction, as represented by most assemblers, loads AL from data segment memory location DATA (1234H). Memory location DATA is a symbolic memory location, while the 1234H is the actual hexadecimal

3–1 DATA-ADDRESSING MODES 63

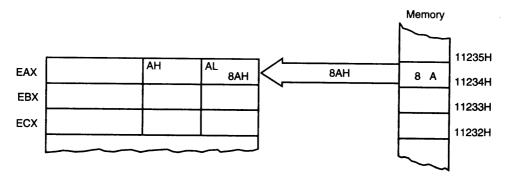

FIGURE 3–5 The operation of the MOV AL,[1234H] instruction when DS = 1000H.

location. With many assemblers, this instruction is represented as a MOV AL,[1234H]<sup>7</sup> instruction. The [1234H] is an absolute memory location that is not allowed by all assembler programs. Note that this may need to be formed as MOV AL,DS:[1234H] with some assemblers, to show that the address is in the data segment. Figure 3–5 shows how this instruction transfers a copy of the byte-sized contents of memory location 11234H into AL. The effective address is formed by adding 1234H (the offset address) to 1000H (the data segment address of 1000H) in a system operating in the real mode.

Table 3–3 lists the three direct addressed instructions. These instructions often appear in programs, so Intel decided to make them special three-byte long instructions to reduce the length of programs. All other instructions that move data from a memory location to a register, called **displacement-addressed instructions**, require four or more bytes of memory for storage in a program.

**Displacement Addressing.** Displacement addressing is almost identical to direct addressing, except that the instruction is four bytes wide instead of three. In the 80386 through the Pentium 4, this instruction can be up to seven bytes wide if a 32-bit register and a 32-bit displacement are specified. This type of direct data addressing is much more flexible because most instructions use it.

If the operation of the MOV CL,DS:[1234H] instruction is compared to that of the MOV AL,DS:[1234H] instruction of Figure 3–5, both basically perform the same operation except for the destination register (CL versus AL). Another difference only becomes apparent upon examining the assembled versions of these two instructions. The MOV AL,DS:[1234H] instruction is three bytes long and the MOV CL,DS:[1234H] instruction is four bytes long, as illustrated in Example 3–4. This example shows how the assembler converts these two instructions into hexadecimal machine language. You must include the segment register DS: in this example, before the [offset] part of the instruction. You may use any segment register, but, in most cases, data are stored in the data segment, so this example uses DS:[1234H].

TABLE 3-3 Direct addressed instructions using AX and AL.

| Assembly Language  | Size    | Operation                                                               |

|--------------------|---------|-------------------------------------------------------------------------|

| MOV AL, NUMBER     | 8-bits  | Copies the byte contents of data segment memory location NUMBER into AL |

| MOV AX,COW         | 16-bits | Copies the word contents of data segment memory location COW into AX    |

| MOV NEWS,AL        | 8-bits  | Copies AL into data segment memory location NEWS                        |

| MOV THERE,AX       | 16-bits | Copies AX into data segment memory location THERE                       |

| MOV ES:[2000 H],AL | 8-bits  | Copies AL into extra data segment memory location 2000H                 |

<sup>&</sup>lt;sup>7</sup>This form may be used with MASM, but most often appears when a program is entered or listed by DEBUG, a debugging toll provided with DOS.

#### **EXAMPLE 3-4**

| 0000 | A0 1234 R    | MOV AL, DS: [1234H] |

|------|--------------|---------------------|

| 0003 | 8A 0E 1234 R | MOV CL, DS: [1234H] |

Table 3–4 lists some MOV instructions, using the displacement form of direct addressing. Not all variations are listed because there are many MOV instructions of this type. The segment registers can be stored or loaded from memory. Example 3–5 shows a short program using models that address information in the data segment. Note that the **data segment** begins with a .DATA statement to inform the assembler where the data segment begins. The model size is adjusted from .TINY, as shown in Example 3–3, to SMALL so that a data segment can be included. The **SMALL model** allows one data segment and one code segment. The SMALL model is often used whenever memory data are required for a program. A SMALL model program assembles as an execute (.EXE) program. Notice how this example allocates memory locations in the data segment by using the DB and DW directives. Here the .STARTUP statement not only indicates the start of the code, but it also loads the data segment register with the segment address of the data segment. If this program is assembled and executed with CodeView, the instructions can be viewed as they execute and change registers and memory locations.

#### **EXAMPLE 3-5**

| 0000                                                                  |                                  | .MODEL               | SMALL                                            | ;select SMALL model<br>;indicate start of DATA segment                                 |

|-----------------------------------------------------------------------|----------------------------------|----------------------|--------------------------------------------------|----------------------------------------------------------------------------------------|

| 0000 10<br>0001 00<br>0002 0000<br>0004 AAAA                          | DATA1<br>DATA2<br>DATA3<br>DATA4 | DB<br>DB<br>DW<br>DW | 10H<br>0<br>0<br>0AAAAH                          | ;place 10H in DATA1<br>;place 0 in DATA2<br>;place 0 in DATA3<br>;place AAAAH in DATA4 |

| 0000                                                                  |                                  | .CODE                | UP                                               | ;indicate start of CODE segment ;indicate start of program                             |

| 0017 A0 0000 R<br>001A 8A 26 0001<br>001E A3 0002 R<br>0021 8B 1E 000 |                                  | MOV<br>MOV<br>MOV    | AL, DATA1<br>AH, DATA2<br>DATA3, AX<br>BX, DATA4 | ·                                                                                      |

|                                                                       |                                  | EXIT<br>END          |                                                  | <pre>;exit to DOS ;end file</pre>                                                      |

TABLE 3-4 Examples of direct data addressing using a displacement.

| Assembly Language             | Size               | Operation                                                                                            |

|-------------------------------|--------------------|------------------------------------------------------------------------------------------------------|

| MOV CH,DOG                    | 8-bits             | Copies the byte contents of data segment memory location DOG into CH                                 |

| MOV CH,[1000H]*               | 8-bits             | Copies the byte contents of data segment offset address 1000H into CH                                |

| MOV ES,DATA6                  | 16-bits            | Copies the word contents of data segment memory location DATA6 into ES                               |

| MOV DATA7,BP<br>MOV NUMBER,SP | 16-bits<br>16-bits | Copies BP into data segment memory location DATA7 Copies SP into data segment memory location NUMBER |

<sup>\*</sup>Note: This form of addressing is seldom used with most assemblers because an actual numeric offset address is rarely accessed.

3–1 DATA-ADDRESSING MODES 65

# **Register Indirect Addressing**

Register indirect addressing allows data to be addressed at any memory location through an offset address held in any of the following registers: BP, BX, DI, and SI. For example, if register BX contains a 1000H and the MOV AX,[BX] instruction executes, the word contents of data segment offset address 1000H are copied into register AX. If the microprocessor is operated in the real mode and DS = 0100H, this instruction addresses a word stored at memory bytes 2000H and 2001H, and transfers it into register AX (see Figure 3–6). Note that the contents of 2000H are moved into AL and the contents of 2001H are moved into AH. The [] symbols denote indirect addressing in assembly language. In addition to using the BP, BX, DI, and SI registers to indirectly address memory, the 80386 and above allow register indirect addressing with any extended register except ESP. Some typical instructions using indirect addressing appear in Table 3–5.

<sup>\*</sup>After DS is appended with a 0.

**FIGURE 3–6** The operation of the MOV AX,[BX] instruction when BX = 1000H and DS = 0100H. Note that this instruction is shown after the contents of memory are transferred to AX.

TABLE 3-5 Example of register indirect addressing.

| Assembly Language | Size    | Operation                                                                          |

|-------------------|---------|------------------------------------------------------------------------------------|

| MOV CX,[BX]       | 16-bits | Copies the word contents of the data segment memory location address by BX into CX |

| MOV [BP],DL*      | 8-bits  | Copies DL into the stack segment memory location addressed by BP                   |

| MOV [DI],BH       | 8-bits  | Copies BH into the data segment memory location addressed by DI                    |

| MOV [DI],[BX]     | _       | Memory-to-memory moves are not allowed except with string instructions             |

<sup>\*</sup>Note: Data addressed by BP are by default located in the stack segment, while all other indirect addressing modes use the data segment by default.

The data segment is used by default with register indirect addressing or any other addressing mode that uses BX, DI, or SI to address memory. If the BP register addresses memory, the stack segment is used by default. These settings are considered the default for these four index and base registers. For the 80386 and above, EBP addresses memory in the stack segment by default; EAX, EBX, ECX, EDX, EDI, and ESI address memory in the data segment by default. When using a 32-bit register to address memory in the real mode, the contents of the 32-bit register must never exceed 0000FFFFH. In the protected mode, any value can be used in a 32-bit register that is used to indirectly address memory, as long as it does not access a location outside of the segment, as dictated by the access rights byte. An example 80386/80486/Pentium 4 instruction is MOV EAX,[EBX]. This instruction loads EAX with the doubleword-sized number stored at the data segment offset address indexed by EBX.

In some cases, indirect addressing requires specifying the size of the data are specified with the **special assembler directive** BYTE PTR, WORD PTR, or DWORD PTR. These directives indicate the size of the memory data addressed by the memory pointer (PTR). For example, the MOV AL,[DI] instruction is clearly a byte-sized move instruction, but the MOV [DI],10H instruction is ambiguous. Does the MOV [DI],10H instruction address a byte-, word-, or double-word-sized memory location? The assembler can't determine the size of the 10H. The instruction MOV BYTE PTR [DI],10H clearly designates the location addressed by DI as a byte-sized memory location. Likewise, the MOV DWORD PTR [DI],10H clearly identifies the memory location as doubleword-sized. The BYTE PTR, WORD PTR, and DWORD PTR directives are used only with instructions that address a memory location through a pointer or index register with immediate data, and for a few other instructions that are described in subsequent chapters.

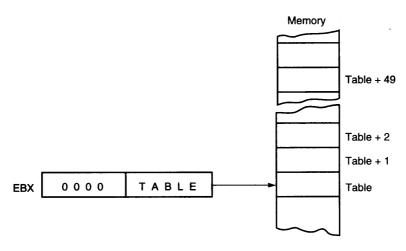

Indirect addressing often allows a program to refer to tabular data located in the memory system. For example, suppose that you must create a table of information that contains 50 samples taken from memory location 0000:046C. Location 0000:046C contains a counter that is maintained by the personal computer's real-time clock. Figure 3–7 shows the table and the BX register used to sequentially address each location in the table. To accomplish this task, load the starting location of the table into the BX register with a MOV immediate instruction. After initializing the starting address of the table, use register indirect addressing to store the 50 samples sequentially.

The sequence shown in Example 3–6 loads register BX with the starting address of the table and initializes the count, located in register CX, to 50. The OFFSET directive tells the assembler to load BX with the offset address of memory location TABLE, not the contents of TABLE. For example, the MOV BX,DATAS instruction copies the contents of memory location DATAS into BX, while the MOV BX,OFFSET DATAS instruction copies the offset address of DATAS into BX. When the OFFSET directive is used with the MOV instruction, the assembler calculates the offset address and then uses a MOV immediate instruction to load the address into the specified 16-bit register.

**FIGURE 3–7** An array (TABLE) containing 50 bytes that are indirectly addressed through register BX.

3–1 DATA-ADDRESSING MODES 67

#### **EXAMPLE 3-6**

| 0000                         |                                    |        | .MODEL SM<br>.DATA        | ALL                            | ;select SMALL model<br>;start of DATA segment                                                         |

|------------------------------|------------------------------------|--------|---------------------------|--------------------------------|-------------------------------------------------------------------------------------------------------|

| 0000                         | 0032 [                             | DATAS  | DW 50                     | DUP (?)                        | ;setup array of 50 bytes                                                                              |

| 0000                         | ·                                  | •      | .CODE                     |                                | ;start of CODE segment<br>;start of program                                                           |

| 0017<br>001A                 | 8E C0<br>B8 0000                   |        | MOV<br>MOV                | AX,0<br>ES,AX                  | ;address segment 0000 with ES                                                                         |

| 001C<br>001F<br>0022         | BB 0000 R<br>B9 0032               | AGAIN: | MOV<br>MOV                | BX,OFFSET DATAS<br>CX,50       | ;address DATAS array<br>;load counter with 50                                                         |

| 0022<br>0026<br>0028<br>0029 | 26:A1 046C<br>89 07<br>43<br>E2 F7 |        | MOV<br>MOV<br>INC<br>LOOP | AX,ES:[046CH] [BX],AX BX AGAIN | <pre>;get clock value ;save clock value in DATAS ;increment BX to next element ;repeat 50 times</pre> |

|                              | _                                  |        | .EXIT                     |                                | <pre>;exit to DOS ;end file</pre>                                                                     |

Once the counter and pointer are initialized, a repeat-until CX = 0 loop executes. Here, data are read from extra segment memory location 46CH with the MOV AX,ES:[046CH] instruction and stored in memory that is indirectly addressed by the offset address located in register BX. Next, BX is incremented (one is added to BX) to the next table location, and finally the LOOP instruction repeats the LOOP 50 times. The LOOP instruction decrements (subtracts one from) the counter (CX); if CX is not zero, LOOP causes a jump to memory location AGAIN. If CX becomes zero, no jump occurs and this sequence of instructions ends. This example copies the most recent 50 values from the clock into the memory array DATAS. This program will often show the same data in each location because the contents of the clock are changed only 18.2 times per second. To view the program and its execution, use the CodeView program. To use CodeView, type CV FILE.EXE or access it as DEBUG from the Programmer's WorkBench program under the RUN menu. Note that CodeView functions only with .EXE or .COM files. Some useful CodeView switches are /50 for a 50-line display and /S for use of high-resolution video displays in an application. To debug the file TEST.COM with 50 lines, type CV /50 TEST.COM at the DOS prompt.

## **Base-Plus-Index Addressing**

Base-plus-index addressing is similar to indirect addressing because it indirectly addresses memory data. In the 8086 through the 80286, this type of addressing uses one base register (BP or BX), and one index register (DI or SI) to indirectly address memory. The base register often holds the beginning location of a memory array, while the index register holds the relative position of an element in the array. Remember that whenever BP addresses memory data, both the stack segment register and BP generate the effective address.

In the 80386 and above, this type of addressing allows the combination of any two 32-bit extended registers except ESP. For example, the MOV DL,[EAX+EBX] instruction is an example using EAX (as the base) plus EBX (as the index). If the EBP register is used, the data are located in the stack segment instead of in the data segment.

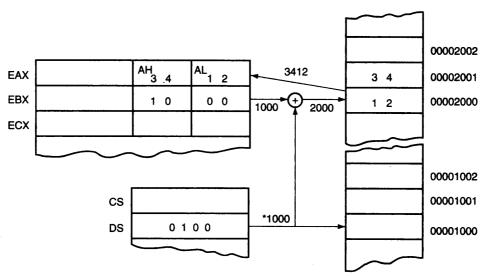

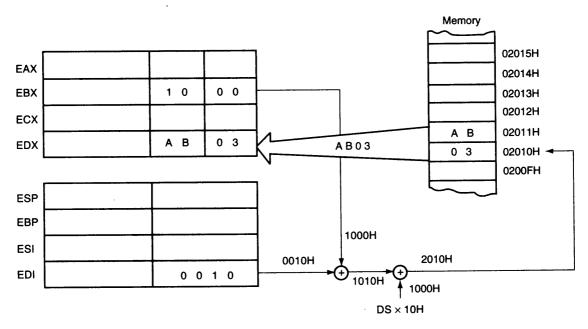

**Locating Data with Base-plus-index Addressing.** Figure 3–8 shows how data are addressed by the MOV DX,[BX+DI] instruction when the microprocessor operates in the real mode. In this example, BX = 1000H, DI = 0010H, and DS = 0100H, which translate into memory address 02010H. This instruction transfers a copy of the word from location 02010H into the DX register. Table 3–6 lists some instructions used for base-plus-index addressing. Note that the Intel assembler requires that this addressing mode appear as [BX][DI] instead of [BX+DI]. The MOV DX,[BX+DI] instruction is MOV DX,[BX][DI] for a program written for the Intel ASM assembler.

**FIGURE 3–8** An example showing how the base-plus-index addressing mode functions for the MOV DX,[BX+DI] instruction. Notice that memory address 02010H is accessed because DS = 0100H, BX =100H, and DI = 0010H.

TABLE 3-6 Examples of base-plus-index addressing.

| Assembly Language | Size    | Operation                                                                                     |

|-------------------|---------|-----------------------------------------------------------------------------------------------|

| MOV CX,[BX+DI]    | 16-bits | Copies the word contents of the data segment memor location address by BX plus DI into CX     |

| MOV CH,[BP+SI]    | 8-bits  | Copies the byte contents of the stack segment memory location addressed by BP plus SI into CH |

| MOV [BX+SI],SP    | 16-bits | • • • • • • • • • • • • • • • • • • •                                                         |

| MOV [BP+DI],AH    | 8-bits  |                                                                                               |

This text uses the first form in all example programs, but the second form can be used in many assemblers, including MASM from Microsoft. Instructions like MOV DI,[BX+DI] will assemble, but will not execute correctly.

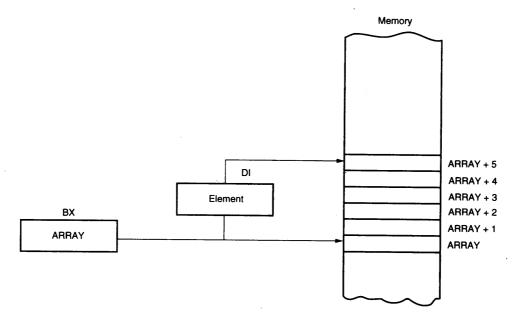

Locating Array Data Using Base-plus-index Addressing. A major use of the base-plus-index addressing mode is to address elements in a memory array. Suppose that the elements in an array, located in the data segment at memory location ARRAY, must be accessed. To accomplish this, load the BX register (base) with the beginning address of the array, and the DI register (index) with the element number to be accessed. Figure 3–9 shows the use of BX and DI to access an element in an array of data.

A short program, listed in Example 3–7, moves array element 10H into array element 20H. Notice that the array element number, loaded into the DI register, addresses the array element. Also notice how the contents of the ARRAY have been initialized so that element 10H contains a 29H.

3–1 DATA-ADDRESSING MODES 69

FIGURE 3–9 An example of the base-plus-index addressing mode. Here an element (DI) of an ARRAY (BX) is addressed.

### **EXAMPLE 3-7**

| 0000                                 |                                                   | .MODEL SMALL<br>.DATA                                                   | ;select SMALL model<br>;start of DATA segment                                                              |

|--------------------------------------|---------------------------------------------------|-------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

| 0000                                 | 0010 [ ARRAY 00                                   | DB 16 DUP (?)                                                           | ;setup ARRAY                                                                                               |

| 0010<br>0011                         | 29<br>001E [<br>00                                | DB 29H<br>DB 30 DUP (?)                                                 | ;sample data at element 10H                                                                                |

| 0000                                 | 1                                                 | .CODE<br>.STARTUP                                                       | <pre>;start of CODE segment ;start of program</pre>                                                        |

| 0017<br>001A<br>001D<br>001F<br>0022 | BB 0000 R<br>BF 0010<br>8A 01<br>BF 0020<br>88 01 | MOV BX,OFFSET ARRAY MOV DI,10H MOV AL,[BX+DI] MOV DI,20H MOV [BX+DI],AL | ;address ARRAY<br>;address element 10H<br>;get element 10H<br>;address element 20H<br>;save in element 20H |

|                                      |                                                   | .EXIT<br>END                                                            | <pre>;exit to DOS ;end of file</pre>                                                                       |

## **Register Relative Addressing**

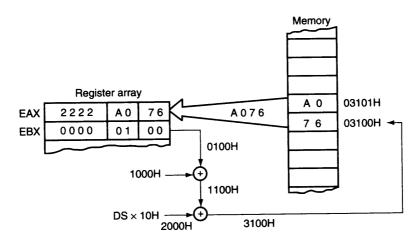

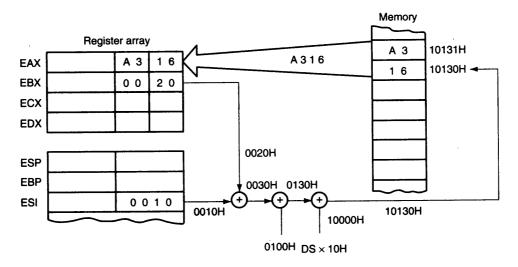

Register relative addressing is similar to base-plus-index addressing and displacement addressing. In register relative addressing, the data in a segment of memory are addressed by adding the displacement to the contents of a base or an index register (BP, BX, DI, or SI). Figure 3–10 shows the operation of the MOV AX,[BX+1000H] instruction. In this example, BX = 0100H and DS = 0200H, so the address generated is the sum of DS  $\times$  10H, BX, and the displacement of 1000H or 03100H. Remember that BX, DI, or SI addresses the data segment and BP addresses the stack segment. In the 80386 and above, the displacement can be a 32-bit number and the register can

**FIGURE 3–10** The operation of the MOV AX,[BX+1000H] instruction, when BX = 0100H and DS = 0200H.

**TABLE 3–7** Examples of register relative addressing.

| Assembly Language | Size    | Operation                                                                                                  |  |

|-------------------|---------|------------------------------------------------------------------------------------------------------------|--|

| MOV AX,[DI+100H]  | 16-bits | Copies the word contents of the data segment memory location addressed by DI plus 100H into AX             |  |

| MOV ARRAY[SI],BL  | 8-bits  | Copies BL into the data segment memory location addressed by ARRAY plus SI                                 |  |

| MOV LIST[SI+2],CL | 8-bits  | Copies CL into the data segment memory location addressed by sum of LIST, SI, and 2                        |  |

| MOV DI,SET_IT[BX] | 16-bits | Copies the word contents of the data segment memory location addressed by the sum of SET_IT and BX into DI |  |

be any 32-bit register except the ESP register. Remember that the size of a real mode segment is 64K bytes long. Table 3-7 lists a few instructions that use register relative addressing.

The displacement can be a number added to the register within the [], as in the MOV AL,[DI+2] instruction, or it can be a displacement subtracted from the register, as in MOV AL,[SI-1]. A displacement also can be an offset address appended to the front of the [], as in MOV AL,DATA[DI]. Both forms of displacements also can appear simultaneously, as in the MOV AL,DATA[DI+3] instruction. In all cases, both forms of the displacement add to the base, or base and index register within the []. In the 8086–80286 microprocessors, the value of the displacement is limited to a 16-bit signed number with a value ranging between +32,767 (7FFFH) and -32,768 (8000H); in the 80386 and above, a 32-bit displacement is allowed with a value ranging between +2,147,483,647 (7FFFFFFFH) and -2,147,483,648 (80000000H).

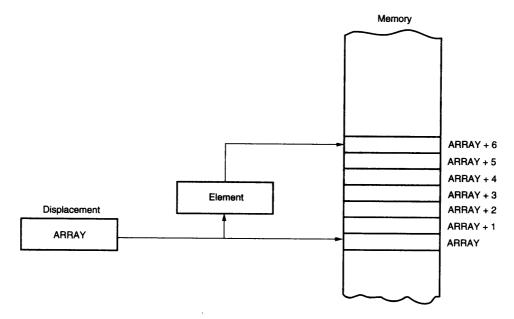

Addressing Array Data with Register Relative. It is possible to address array data with register relative addressing, such as one does with base-plus-index addressing. In Figure 3–11, register relative addressing is illustrated with the same example as for base-plus-index addressing. This shows how the displacement ARRAY adds to index register DI to generate a reference to an array element.

**FIGURE 3–11** Register relative addressing used to address an element of ARRAY. The displacement addresses the start of ARRAY, and DI accesses an element.

Example 3-8 shows how this new addressing mode can transfer the contents of array element 10H into array element 20H. Notice the similarity between this example and Example 3-7. The main difference is that, in Example 3-8, register BX is not used to address memory area ARRAY; instead, ARRAY is used as a displacement to accomplish the same task.

### **EXAMPLE 3-8**

| 0000                         |                                                |          | ODEL SMALL<br>ATA       | ;select SMALL model<br>;start of DATA segment                                            |

|------------------------------|------------------------------------------------|----------|-------------------------|------------------------------------------------------------------------------------------|

| 0000                         | 0010 [ 00                                      | ARRAY DB | 16 DUP (?)              | ;setup ARRAY                                                                             |

| 0010<br>0011                 | 29<br>001E [<br>00                             | DB DB    | 29H<br>30 DUP (?)       | ;sample data at element 10H                                                              |

| 0000                         |                                                | _        | DDE<br>FARTUP           | ;start of CODE segment<br>;start of program                                              |

| 0017<br>001A<br>001E<br>0021 | BF 0010<br>8A 85 0000<br>BF 0020<br>88 85 0000 | MO       | AL, ARRAY[DI] J DI, 20H | ;address element 10H<br>;get element 10H<br>;address element 20H<br>;save in element 20H |

|                              |                                                | . EX     | KIT<br>O                | <pre>;exit to DOS ;end of file</pre>                                                     |

### **Base Relative-Plus-Index Addressing**

The base relative-plus-index addressing mode is similar to the base-plus-index addressing mode, but it adds a displacement, besides using a base register and an index register, to form the memory address. This type of addressing mode often addresses a two-dimensional array of memory data.

Addressing Data with Base Relative-plus-index. Base relative-plus-index addressing is the least-used addressing mode. Figure 3–12 shows how data are referenced if the instruction executed by the microprocessor is a MOV AX,[BX+SI+100H]. The displacement of 100H adds to BX and SI to form the offset address within the data segment. Registers BX = 0020H, SI = 0010H, and DS = 1000H, so the effective address for this instruction is 10130H—the sum of these registers plus a displacement of 100H. This addressing mode is too complex for frequent use in a program. Some typical instructions using base relative-plus-index addressing appear in Table 3–8. Note that with the 80386 and above, the effective address is generated by the sum of two 32-bit registers plus a 32-bit displacement.

**FIGURE 3–12** An example of base relative-plus-index addressing using a MOV AX,[BX+SI+100H] instruction. Note: DS = 1000H.

**TABLE 3–8** Example base relative-plus-index instructions.

| Assembly Language    | Size    | Operation                                                                                                     |  |

|----------------------|---------|---------------------------------------------------------------------------------------------------------------|--|

| MOV DH,[BX+DI+20H]   | 8-bits  | Copies the byte contents of the data segment memory location addressed by the sum of BX, DI, and 20H into DH  |  |

| MOV AX,FILE[BX+DI]   | 16-bits | Copies the word contents of the data segment memory location addressed by the sum of FILE, BX, and DI into AX |  |

| MOV LIST[BP+DI],CL   | 8-bits  | Copies CL into the stack segment memory location addressed by the sum of LIST, BP, and DI                     |  |

| MOV LIST[BP+SI+4],DH | 8-bits  | Copies DH into the stack segment memory location addressed by the sum of LIST, BP, SI, and 4                  |  |

**FIGURE 3–13** Base relative-plus-index addressing used to access a FILE that contains multiple records (REC).

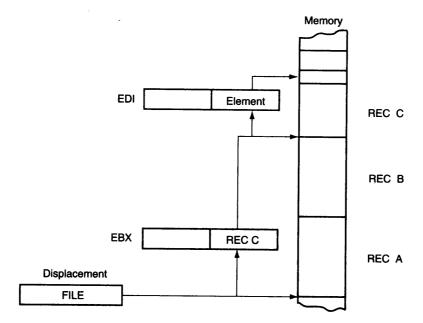

**Addressing Arrays with Base Relative-plus-index.** Suppose that a file of many records exists in memory and each record contains many elements. This displacement addresses the file, the base register addresses a record, and the index register addresses an element of a record. Figure 3–13 illustrates this very complex form of addressing.

Example 3–9 provides a program that copies element 0 of record A into element 2 of record C by using the base relative-plus-index mode of addressing. This example FILE contains four records and each record contains 10 elements. Notice how the THIS BYTE statement is used to define the label FILE and RECA as the same memory location.

#### **EXAMPLE 3-9**

| 0000              | .MODEL SMALL<br>.DATA | ;SMALL model<br>;start of DATA segment      |

|-------------------|-----------------------|---------------------------------------------|

| 0000 = 0000       | FILE EQU THIS BYTE    | assign FILE to this byte;                   |

| ] A000 0000       | RECA DB 10 DUP (?)    | ;reserve 10 bytes for RECA                  |

| ] A000 A000<br>00 | RECB DB 10 DUP (?)    | ;reserve 10 bytes for RECB                  |

| 0014 000A [       | RECC DB 10 DUP (?)    | ;reserve 10 bytes for RECC                  |

| 001E 000A [       | RECD DB 10 DUP (?)    | ;reserve 10 bytes for RECD                  |

| 0000              | .CODE<br>.STARTUP     | ;start of CODE segment<br>;start of program |

#### 74 CHAPTER 3 ADDRESSING MODES

| 0017<br>001A<br>001D<br>0021<br>0024<br>0027 | BB 0000 R<br>BF 0000<br>8A 81 0000 R<br>BB 0014 R<br>BF 0002<br>88 81 0000 R | MOV<br>MOV<br>MOV<br>MOV<br>MOV | BX,OFFSET RECA<br>DI,0<br>AL,FILE[BX+DI]<br>BX,OFFSET RECC<br>DI,2<br>FILE[BX+DI],AL | ;address RECA<br>;address element 0<br>;get data<br>;address RECC<br>;address element 2<br>;save data |

|----------------------------------------------|------------------------------------------------------------------------------|---------------------------------|--------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

|                                              |                                                                              | .EXIT                           |                                                                                      | exit to DOS; end of file                                                                              |

## **Scaled-Index Addressing**

Scaled-index addressing is the last type of data-addressing mode discussed. This data-addressing mode is unique to the 80386 through the Pentium 4 microprocessors. Scaled-index addressing uses two 32-bit registers (a base register and an index register) to access the memory. The second register (index) is multiplied by a scaling factor. The scaling factor can be 1X, 2X, 4X, or 8X. A scaling factor of 1X is implied and need not be included in the assembly language instruction (MOV AL,[EBX+ECX]). A scaling factor of 2X is used to address word-sized memory arrays, a scaling factor of 4X is used with doubleword-sized memory arrays, and a scaling factor of 8X is used with quadword-sized memory arrays.

An example instruction is MOV AX,[EDI+2\*ECX]. This instruction uses a scaling factor of 2X, which multiplies the contents of ECX by 2 before adding it to the EDI register to form the memory address. If ECX contains a 00000000H, word-sized memory element 0 is addressed; if ECX contains a 00000001H, word-sized memory element 1 is accessed, and so forth. This scales the index (ECX) by a factor of 2 for a word-sized memory array. Refer to Table 3–9 for some examples of scaled-index addressing. As you can imagine, there are an extremely large number of the scaled-index addressed register combinations. Scaling is also applied to instructions that use a single indirect register to access memory. The MOV EAX,[4\*EDI] is a scaled-index instruction that uses one register to indirectly address memory.

Example 3–10 shows a sequence of instructions that uses scaled-index addressing to access a word-sized array of data called LIST. Note that the offset address of LIST is loaded into register EBX with the MOV EBX,OFFSET LIST instruction. Once EBX addresses array LIST, the elements (located in ECX) of 2, 4, and 7 of this word-wide array are added, using a scaling factor of 2 to access the elements. This program stores the 2 at element 2 into elements 4 and 7. Also notice the .386 directive to select the 80386 microprocessor. This directive must follow the .MODEL statement for the assembler to process 80386 instructions for DOS. If the 80486 is in use, the .486 directive appears after the .MODEL statement; if the Pentium, Pentium Pro, Pentium II, Pentium III,

TABLE 3-9 Examples of scaled-index addressing. (Not for 8086/ 8088/80286 readers).

| Assembly Language       | Size    | Operation                                                                                                                  |

|-------------------------|---------|----------------------------------------------------------------------------------------------------------------------------|

| MOV EAX,[EBX+4*ECX]     | 32-bits | Copies the doubleword contents of the data segment memory location addressed by the sum of 4 times ECX plus EBX into       |

|                         |         | EAX                                                                                                                        |

| MOV [EAX+2*EDI+100H],CX | 16-bits | Copies CX into the data segment memory location addressed by the sum of EAX, 100H, and 2 times EDI                         |

| MOV AL,[EBP+2*EDI-2]    | 8-bits  | Copies the byte contents of the stack segment memory location addressed by the sum of EBP, -2, and 2 times EDI into AL     |

| MOV EAX,ARRAY[4*ECX]    | 32-bits | Copies the doubleword contents of the data segment memory location addressed by the sum of ARRAY plus 4 times ECX into EAX |

3–1 DATA-ADDRESSING MODES 75

or Pentium 4 is in use, the .586 directive appears after .MODEL. If the microprocessor selection directive appears before the .MODEL statement, the microprocessor executes instructions in the 32-bit mode, which is not compatible with DOS.

#### **EXAMPLE 3-10**

| 0000         |                                 | .MODEL SMALL<br>.386<br>.DATA   | ;select SMALL model<br>;use the 80386<br>;start of DATA segment |

|--------------|---------------------------------|---------------------------------|-----------------------------------------------------------------|

| 0000         | 0000 0001 0002 LIST 0003 0004   | · · · · · · · · ·               | ;define array list                                              |

| 000A         | 0005 0006 0007<br>0008 0009     | DW 5,6,7,8,9                    |                                                                 |

| 0000         |                                 | .CODE<br>.STARTUP               | ;start of CODE segment<br>;start of program                     |

| 0010         | 66  BB 00000000 R               | MOV EBX,OFFSET LIST             |                                                                 |

| 0016<br>001C | 66  B9 00000002<br>67& 8B 04 4B | MOV ECX,2<br>MOV AX,[EBX+2*ECX] | ;get element 2                                                  |

| 0020<br>0026 | 66  B9 00000004<br>67& 89 04 4B | MOV ECX,4<br>MOV [EBX+2*ECX],AX | ;store in element 4                                             |

| 002A<br>0030 | 66  B9 00000007<br>67& 89 04 4B | MOV ECX,7<br>MOV [EBX+2*ECX],AX | ;store in element 7                                             |

|              |                                 | .EXIT                           | <pre>;exit to DOS ;end of file</pre>                            |

## **Data Structures**

A data structure is used to specify how information is stored in a memory array and can be quite useful with applications that use arrays. It is best to think of a data structure as a template for data. The start of a structure is identified with the STRUC assembly language directive and the end with the ENDS statement. A typical data structure is defined and used three times in Example 3–11. Notice that the name of the structure appears with the STRUC and with ENDS statement.

### **EXAMPLE 3-11**

| 0057 |      |    | ;Defin<br>INFO | e INFO<br>STRU | data structure<br>C |                       |

|------|------|----|----------------|----------------|---------------------|-----------------------|

| 0000 | 0020 | 00 | NAMES          | DB             | 32 DUP (?)          | ;32 bytes for name    |

| 0020 | 0020 | 00 | STREET         | DB             | 32 DUP (?)          | ;32 bytes for street  |

| 0040 | 0010 | 00 | CITY           | DB             | 16 DUP (?)          | ;16 bytes for city    |

| 0050 | 0002 | 00 | STATE          | DB             | 2 DUP (?)           | ;2 bytes for state    |

| 0052 | 0005 | 00 | ZIP            | DB             | 5 DUP (?)           | ;5 bytes for zip-code |

|      |      | ]  | INFO           | ENDS           |                     |                       |

```

<'Bob Smith','123 Main Street','Wanda','OH','44444'>

0000 42 6F 62 20 53 6D NAME1 INFO

69 74 68

0017 [

1

31 32 33 20 4D

61 69 6E 20 53 74

72 65 65 74

0011 [

57 61 6E 64 61

000B [

1

4F 48 34 34 34

34 34

0057 53 74 65 76 65 20 NAME2 INFO <'Steve Doe','222 Mouse Lane','Miller','PA','18100'>

44 6F 65

0017 [

00

32 32 32 20 4D

6F 75 73 65 20 4C 61 6E 65

0012 [

00

4D 69 6C 6C 65

72

] A000

00

50 41 31 38 31

30 30

00AE 42 65 6E 20 44 6F NAME3 INFO <'Jim Dover','303 Main Street','Orender','CA','90000'>

76 65 72

0017 [

00

33 30 33 20 4D

61 69 6E 20 53 74

72 65 65 74

0011 [

4F 72 65 6E 64

65 72

0009 [

43 41 39 30 30

```

The data structure in Example 3–11 defines five fields of information. The first is 32 bytes long and holds a name; the second is 32 bytes long and holds a street address; the third is 16 bytes long for the city; the fourth is 2 bytes long for the state; the fifth is 5 bytes long for the ZIP Code. Once the structure is defined (INFO), it can be filled, as illustrated, with names and addresses. Three examples of uses for INFO are illustrated. Note that literals are surrounded with apostrophes and the entire field is surrounded with < > symbols when the data structure is used to define data.

When data are addressed in a structure, use the structure name and the field name to select a field from the structure. For example, to address the STREET in NAME2, use the operand NAME2.STREET, where the name of the structure is first followed by a period and then by the name of the field. Likewise, use NAME3.CITY to refer to the city in structure NAME3.

#### **EXAMPLE 3-12**

```

;Clear names in array NAME1

0000 B9 0020

MOV

CX,32

0003

B0 00

MOV

AL,0

0005

BE 0000 R

MOV

SI, OFFSET NAME1. NAMES

0008 F3/AA

REP

STOSB

;Clear street in array NAME2

000A B9 0020

MOV

CX,32

000D B0 00

MOV

AL,0

0010

BE 0077 R

MOV

SI, OFFSET NAME2.STREET

0013

F3/AA

REP

STOSB

;Clear zip-code in array NAME3

0015

B9 0005

MOV

CX,5

0018 B0 00

MOV

AL,0

001A BE 0100 R

MOV

SI, OFFSET NAME3.ZIP

001D

F3/AA

REP

STOSB

```